RETROSPECTIVE: Aladdin: a Pre-RTL, Power-Performance Accelerator Simulator Enabling Large Design Space Exploration of Customized Architectures | Semantic Scholar

OGAWA, Tadashi on X: "=> "SMAUG: End-to-End Full-Stack Simulation Infrastructure for Deep Learning Workloads", Harvard, ACM TACO, Nov 2020 https://t.co/qbXsrb383v Simulating ML Appls Using gem5-Aladdin https://t.co/iZXsVn0mzt S Xi, PhD Thesis, 2018 ...

GitHub - alan-turing-institute/gem5-aladdin-boat: End-to-end SoC simulation: integrating the gem5 system simulator with the Aladdin accelerator simulator.

![PDF] Co-designing accelerators and SoC interfaces using gem5-Aladdin | Semantic Scholar PDF] Co-designing accelerators and SoC interfaces using gem5-Aladdin | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/418d9dc849e6a561f3128568864734f5dc106385/2-Figure1-1.png)

![PDF] Co-designing accelerators and SoC interfaces using gem5-Aladdin | Semantic Scholar PDF] Co-designing accelerators and SoC interfaces using gem5-Aladdin | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/418d9dc849e6a561f3128568864734f5dc106385/2-Figure2-1.png)

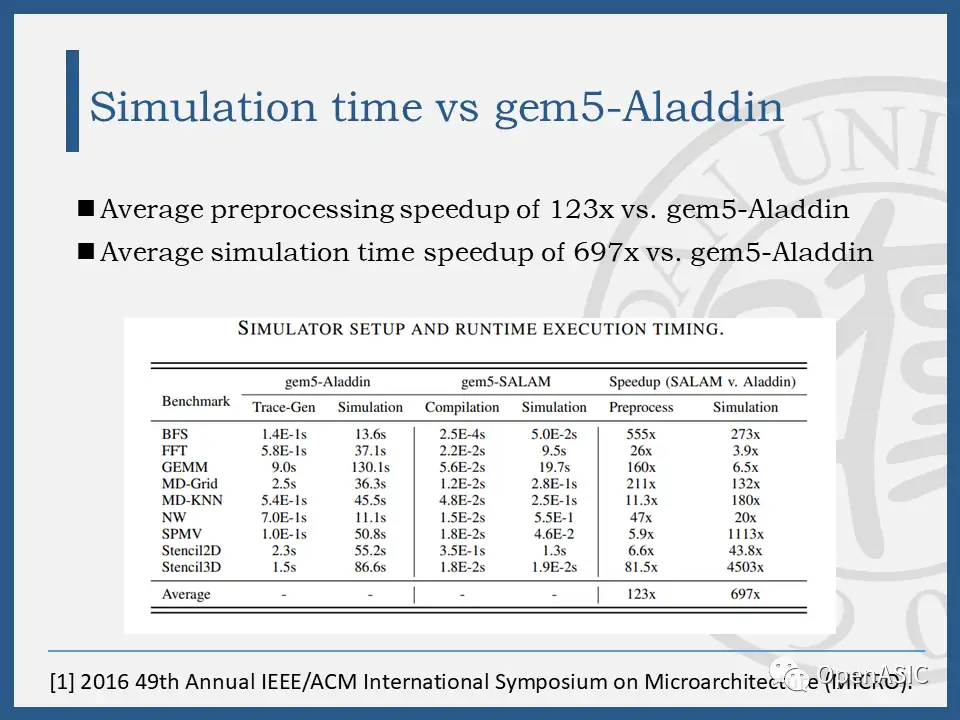

![PDF] gem5-SALAM: A System Architecture for LLVM-based Accelerator Modeling | Semantic Scholar PDF] gem5-SALAM: A System Architecture for LLVM-based Accelerator Modeling | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/fc1c92cbcab66d04e9dd59a429cf250c3efbf28f/9-TableIV-1.png)